…

…

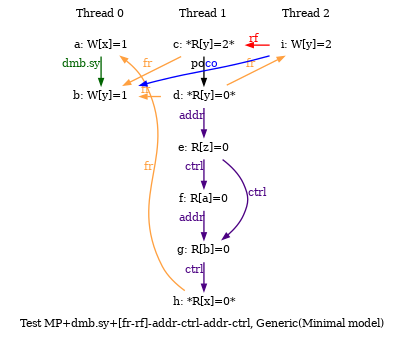

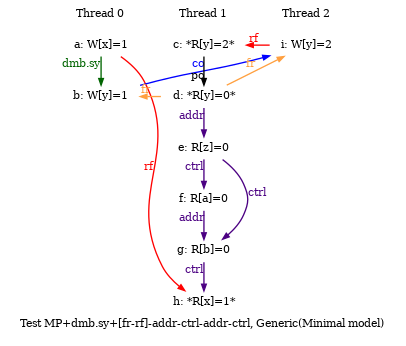

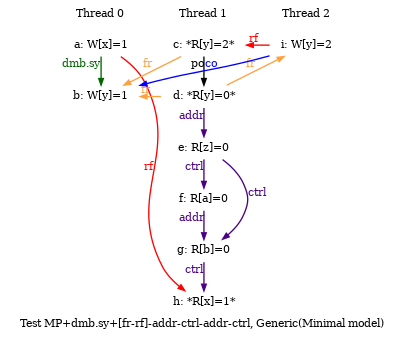

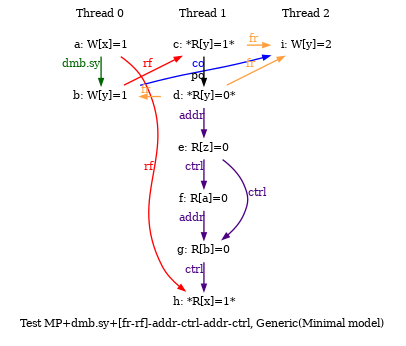

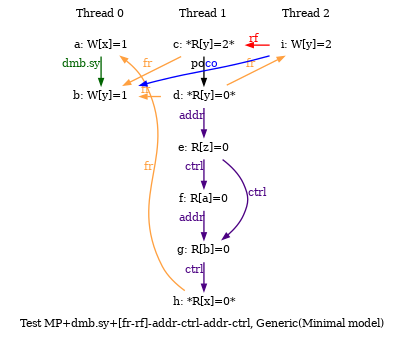

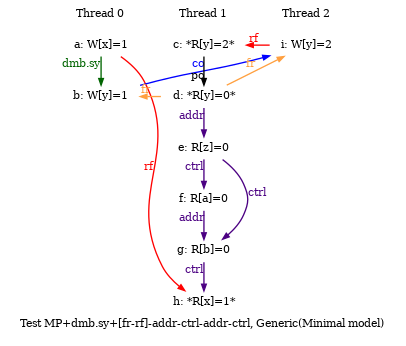

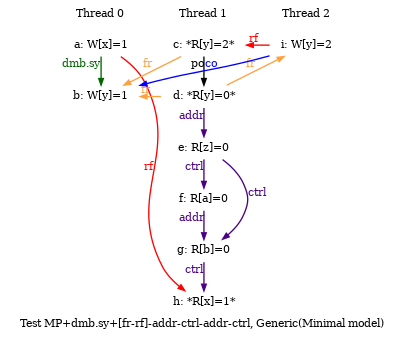

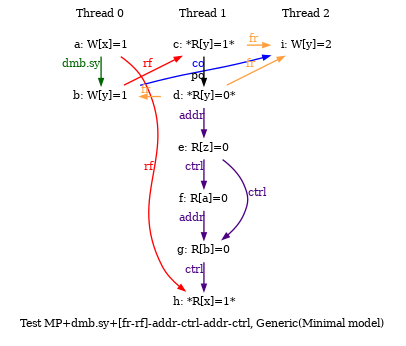

AArch64 MP+dmb.sy+[fr-rf]-addr-ctrl-addr-ctrl

"DMB.SYdWW Rfe FrLeave RfBack DpAddrdR DpCtrldR DpAddrdR DpCtrldR Fre"

Cycle=Rfe FrLeave RfBack DpAddrdR DpCtrldR DpAddrdR DpCtrldR Fre DMB.SYdWW

Relax=

Safe=Rfe Fre DMB.SYdWW DpAddrdR DpCtrldR [FrLeave,RfBack]

Prefetch=0:x=F,0:y=W,1:y=F,1:x=T

Com=Rf Fr Rf

Orig=DMB.SYdWW Rfe FrLeave RfBack DpAddrdR DpCtrldR DpAddrdR DpCtrldR Fre

{

0:X1=x; 0:X3=y;

1:X1=y; 1:X5=z; 1:X7=a; 1:X10=b; 1:X12=x;

2:X1=y;

}

P0 | P1 | P2 ;

MOV W0,#1 | LDR W0,[X1] | MOV W0,#2 ;

STR W0,[X1] | LDR W2,[X1] | STR W0,[X1] ;

DMB SY | EOR W3,W2,W2 | ;

MOV W2,#1 | LDR W4,[X5,W3,SXTW] | ;

STR W2,[X3] | CBNZ W4,LC00 | ;

| LC00: | ;

| LDR W6,[X7] | ;

| EOR W8,W6,W6 | ;

| LDR W9,[X10,W8,SXTW] | ;

| CBNZ W9,LC01 | ;

| LC01: | ;

| LDR W11,[X12] | ;

Observed

y=2; x=1; 1:X2=0; 1:X11=1; 1:X0=2;

and y=1; x=1; 1:X2=0; 1:X11=1; 1:X0=2;

and y=1; x=1; 1:X2=0; 1:X11=0; 1:X0=2;

and y=1; x=1; 1:X2=2; 1:X11=1; 1:X0=1;

and y=2; x=1; 1:X2=0; 1:X11=1; 1:X0=1;

and y=1; x=1; 1:X2=0; 1:X11=1; 1:X0=1;

…

…